智慧型手機、平板裝置的運算技術與功能發展不斷演進,已有逐步取代個人電腦(PC)的趨勢;然而,人們對產品性能的要求愈來愈高,並希望使用時間可再延長,降低充電次數,因此須縮減其中耗電比例較高的應用處理器或基頻晶片功耗,導致晶片架構與製程演進變得非常重要,相關業者須同時兼顧處理器高效能與低耗電量,才能延長裝置待機時間。

因此,相關晶片商正加快處理器製程演進腳步,期以最先進製程,在相同的晶片單位面積下,達到最佳效能與最低能耗。

轉向閘極後製 Intel/台積電製程領先

現階段最先進且可量產的製程技術非28奈米HKMG製程莫屬,可有效提升閘極控制能力,改善晶片漏電流情形。相較之下,過往晶圓廠均以二氧化矽(SiO2)或氮氧化矽(SiON)做為閘極的氧化層,相關電容計算公式為:C=ε_0,ε,S/D,其中ε_0、ε為空氣與材料的介電係數,S與D分別為閘極表面積以及氧化層厚度。

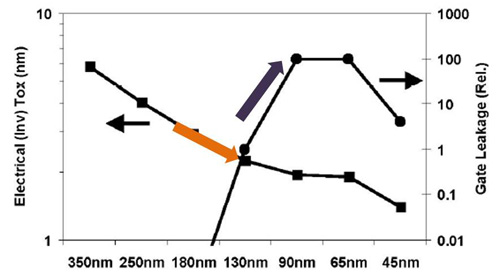

隨著電晶體線寬微縮,為達到相同的電容值,就須降低氧化層厚度,導致等效氧化厚度(Equivalent Oxide Thickness, EOT)愈來愈薄,閘極控制開關能力下降,漏電流上升(圖1),並造成多餘的能耗與電性量測上的飄移,良率也大幅下降。

|

| 圖1 在各個技術節點下,閘極氧化層與漏電流的關係。 |

根據公式,選擇較高介電係數材料係當下能維持相同氧化層電容值的唯一辦法。其中,英特爾(Intel)於2007年就已將HKMG技術應用在45奈米製程節點,以有效降低閘極的維持電壓,並維持相同的閘極控制能力,進而降低元件耗電量。

自英特爾引領風潮後,相關元件商或晶圓代工廠也希望利用此技術量產晶片,以同時達成高效能與低功耗目的。然而,目前全球可大量提供28奈米結合HKMG製程且良率穩定的廠商,主要仍以台積電與英特爾為主,探究其技術領先的原因,主要是製程流程上的先後順序不同。

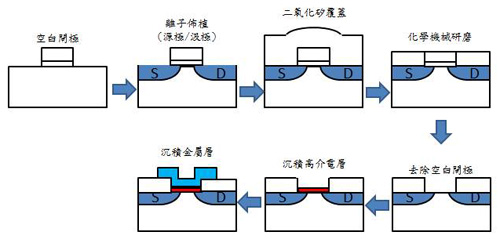

傳統製程流程皆為閘極優先製程(Gate First),圖2為製造流程示意圖。過去使用SiO2或SiON當氧化層材料時,因其具有對熱及化學的穩定性,可容忍較高的回火(Annealing)條件;但是,改用高介電係數材料後,因氧化層與金屬層有熱預算(Thermal Budget)的問題,在高溫回火時,會間接造成等效氧化層厚度增加,其熱預算的障礙便提高閘極優先製程在製程微縮上的困難度。

|

| 圖2 閘極優先流程圖 |

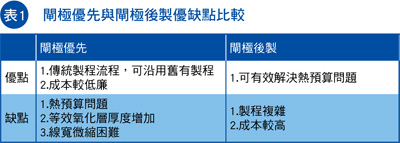

為解決此一問題,英特爾率先運用雷射回火(Laser Annealing)及閘極後製(Gate Last)製程,將此技術應用在其自家45奈米製程產品上,製作流程如圖3所示。在閘極後製製程中,先進行離子布植製程與高溫退火,再沉積高介電層,此來雖能避免高介電層的熱預算問題,但相較於閘極優先製程,製程程序上多出不少步驟,因而也大幅增加生產成本,如表1為閘極優先與後製的相關比較。

|

| 圖3 閘極後製流程圖 |

|

由上述比較可了解,如要進行線寬微縮,閘極後製製程較閘極優先會較為容易,前文提到目前全球可大量供應28奈米結合HKMG的廠商為台積電與英特爾,就是因為選擇閘極後製製程,其他廠商如三星(Samsung)、聯電與格羅方德(GLOBALFOUNDRIES)等,則繼續採用閘極優先製程,故在28奈米製程競爭上落後給台積電與英特爾。

電晶體漏電流再降 晶圓廠競逐FinFET技術

電晶體漏電流再降 晶圓廠競逐FinFET技術

未來,電晶體線寬仍將持續微縮,儘管目前閘極控制能力下降所造成的漏電流問題,已能藉由HKMG技術克服,但是,電晶體電流通道的漏電流影響還是存在;因此,隨著電晶體的體積愈來愈小,電流通道愈來愈短,閘極無法有效控制電晶體電流流動,以及通道漏電流問題將更加嚴重,稱為短通道效應(Short-Channel Effect)。

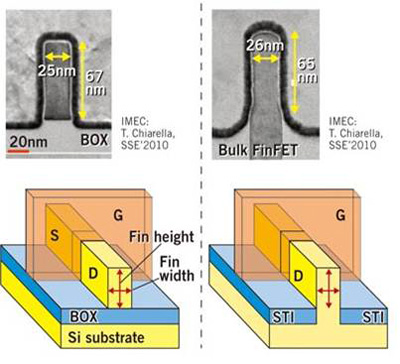

此一問題在平面式的電晶體架構中正逐漸被突顯出來,因此英特爾於2012年公開發表的22奈米製程節點產品,開始導入立體式電晶體結構,並命名為三閘極(Tri-Gate)電晶體;利用立體結構可加強閘極對通道的控制能力,並可將通道內的電流完全耗盡,降低漏電流產生,同時亦能降低操作電壓。其中,該技術由於製程使用矽晶圓的不同,主要可分為兩類,首先是絕緣層覆矽鰭式電晶體(FinFET on SOI)與塊狀基板式鰭式電晶體(Bulk FinFET),圖4為兩種結構的示意圖。

|

| 圖4 左圖為SOI FinFET;右圖為Bulk FinFET |

這兩種製程的主要差別在於使用不同的矽晶圓,造成製程上難易度不同。SOI FinFET技術供應商考量立體電晶體結構須嚴格控制通道雜質摻雜濃度,遂於晶圓製造時即嚴格控制雜質均勻度;相較之下,Bulk FinFET通道雜質則於製程進行時摻雜,參數控制困難。

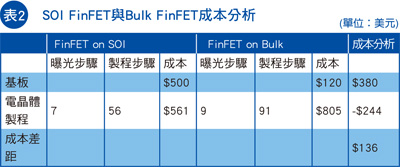

也因此,SOI FinFET的製程流程步驟與難易度較Bulk FinFET簡短與容易;惟SOI FinFET的晶圓成本較高,將加重總體製程成本,且晶圓廠對Bulk FinFET製程較熟悉,亦可縮短量產時程,因此兩種製程各有利弊,相關比較如表2。

|

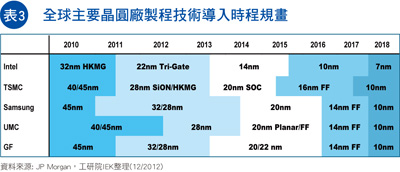

表3則為全球各大晶圓製造廠的開發進度,目前技術開發進度最快的仍是英特爾,其已發表立體式結構電晶體並正展開量產,緊追在後的為台積電,但在20奈米製程節點將繼續使用平面式電晶體,而非立體式,應是希望在現有製程平台上延伸現有技術,以降低研發與設備採購成本,預計16奈米才會導入立體式結構電晶體的生產。

|

突破製程演進關卡 半導體材料革新潮將至

除製程演進外,半導體材料也將掀起革新風潮。歐洲半導體研究機構–比利時微電子研究中心(IMEC),公布的未來電晶體發展藍圖指出,目前主流製程已進入32/28奈米HKMG階段,後續發展至16/14奈米將採用立體結構的電晶體,緊接著進入10奈米以下節點,則可能改搭三五族(III-V)及鍺(Ge)做為電晶體通道材料,引爆新一波半導體技術革命。

目前主流的邏輯電路為互補式金屬氧化物半導體(CMOS),由N型與P型MOS元件構成,因其特性上具有互補的效果,故稱為CMOS。其中,NMOS由閘極開關施以一操作電壓,形成一電子通道進行導通,相對的,PMOS是由閘極開關施以一操作電壓,形成一電洞通道進行導通;過去晶圓代工業者均摻雜(Doping)不同雜質的矽做為通道材料,但為提升電晶體效能,增加通道遷移率(Channel Mobility),改變通道材質已是未來重要的參考選項。

由於III-V族半導體晶圓材料可提供較矽高出十到三十倍的電子遷移率(Electron Mobility),將成為高速且低功率n通道產品的優良候選;但對於p通道產品來說,由於III-V族材料的電洞遷移率(Hole Mobility)相當低,反而不是一個好的選擇,另一種電洞遷移率約為矽四倍以上的鍺,將在此類應用脫穎而出。

但是,改用非矽通道材料有其技術挑戰;過去,矽晶圓幾乎是完美的單晶結構,如欲植入均勻的新材料將非常困難,主要原因是由於各種材料的熱膨脹係數、晶格常數及晶型均有所差異,將使III-V族材料的摻雜製程面臨巨大挑戰。近年產學界雖不斷努力提出研究成果,逐漸克服製程種種困難,但部分的潛在障礙依舊等待解決,故距離商用量產還須一段時間。

半導體技術投資擴大 廠商策略聯盟將成顯學

顯而易見,全球晶圓製造廠無不使出渾身解數延伸摩爾定律(Moore’s Law),但隨著線寬微縮,半導體亦逐漸遭遇到物理極限的限制,例如短通道效應、閘極氧化層過薄造成的漏電流,或III-V族及鍺等通道材料換新的問題。

可以想見的是,在市場對晶片製程微縮需求殷切之下,未來半導體產業將面臨的問題只會多不會少,且生產成本也會不斷提升。如此一來,單家公司可能無法面對過於龐大的研發成本,導致策略聯盟模式將愈來愈常見;因應此趨勢,不論是在設備、材料或製程技術發展上的結盟,台灣政府均須未雨綢繆,積極扮演產業監督、媒合與協助的角色,才能帶動國內半導體產業技術成長,持續提升市場競爭力。